Especificació

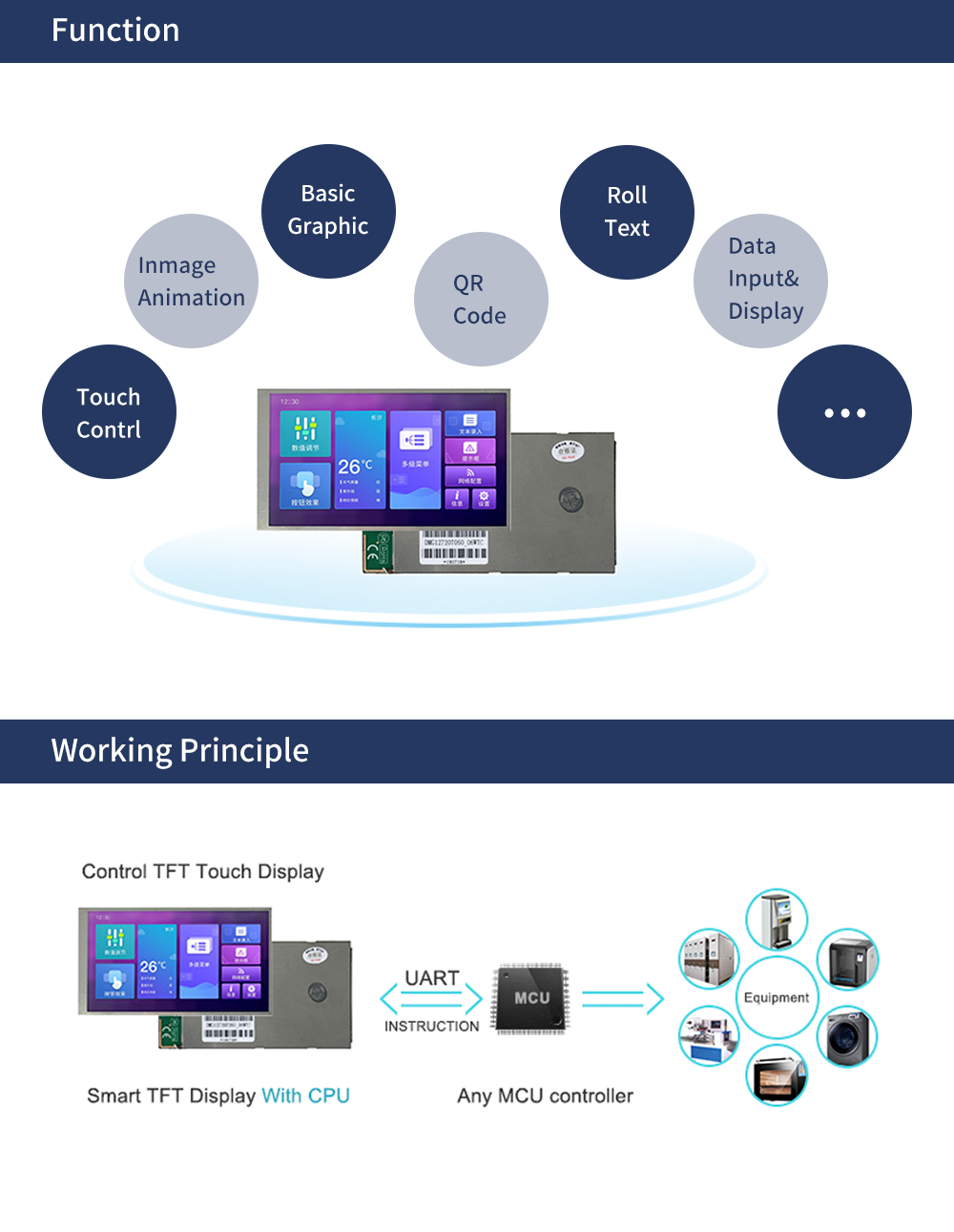

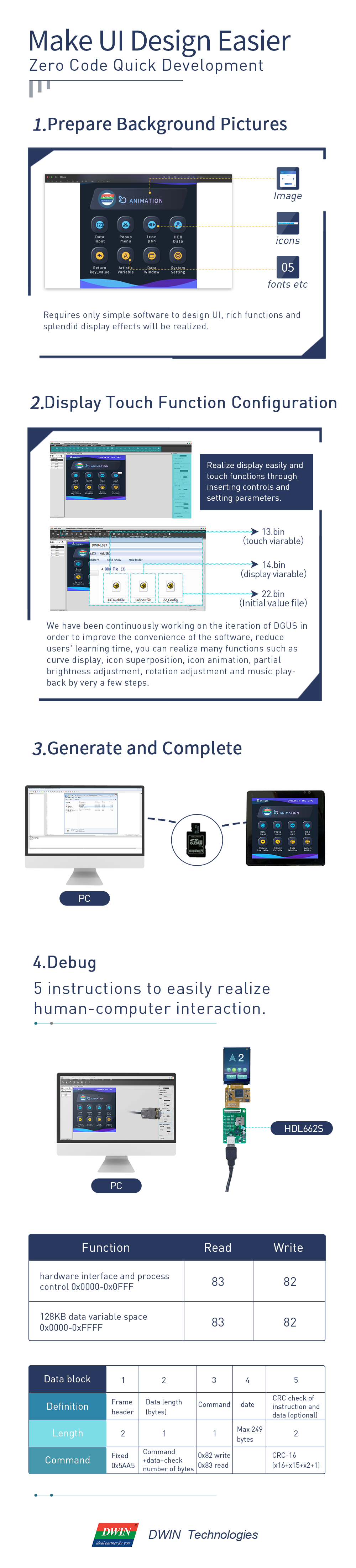

| T5L0 ASIC | El T5L0 ASIC és un ASIC de doble nucli d'un sol xip i una aplicació de baix consum, rendible, altament integrat i dissenyat per DWIN Technology per a LCD de mida petita i produït en massa el 2020. | ||

| Color | 262K colors | ||

| Tipus LCD | IPS-TFT-LCD | ||

| Angle de visió | Àngel de visió ample, valor típic de 85°/85°/85°/85° (L/R/U/D) | ||

| Àrea de visualització (AA) | 71,86 mm (ample) × 70,18 mm (altura) | ||

| Resolució | 480*480 | ||

| Llum de fons | LED | ||

| Brillantor | DMG48480F040_01WTC:200nit DMG48480F040_01WTCZ01:200nit DMG48480F040_01WTCZ02:50nit DMG48480F040_01WN:250nit | ||

| Tipus | CTP (Panell tàctil capacitiu) | ||

| Estructura | Estructura G+G | ||

| Mode tàctil | Punt de suport tàctil i arrossegament | ||

| Duresa superficial | 6H | ||

| Transmissió de la llum | Més del 90% | ||

| La vida | Més d'1.000.000 de vegades de tocar | ||

| Tensió d'alimentació | 3,6 ~ 5,5 V, valor típic de 5 V | ||

| Corrent de funcionament | 245mA, VCC=5V, llum de fons màxima | ||

| 75 mA, VCC=5V, retroil·luminació apagada | |||

| Temperatura de treball | -10 ~ 60 ℃ |

| Temperatura del magatzem | -20 ~ 70 ℃ |

| Humitat de treball | 10% ~ 90% HR |

| Interfície d'usuari | 50Pin_0,5 mm FPC | ||

| Velocitat de transmissió | 3150~3225600bps | ||

| Tensió de sortida | Sortida 1; 3,0 ~ 3,3 V | ||

| Sortida 0;0~0,3 V | |||

| Voltatge d'entrada (RXD) | Entrada 1; 3,3 V | ||

| Entrada 0;0~0,5V | |||

| Interfície | UART2: TTL; UART4: TTL; (Només disponible després de la configuració del sistema operatiu) UART5: TTL; (Només disponible després de la configuració del sistema operatiu | ||

| Format de dades | UART2: N81; UART4: N81/E81/O81/N82; 4 modes (configuració del sistema operatiu) UART5: N81/E81/O81/N82; 4 modes (configuració del sistema operatiu) | ||

| Pin | Definició | E/S | Descripció funcional |

| 1 | 5V | I | Font d'alimentació, DC3.6-5.5V |

| 2 | 5V | I | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | AD7 | I | 5 ADC d'entrada.Resolució de 12 bits en cas d'alimentació de 3,3 V.Tensió d'entrada 0-3,3 V.Excepte l'AD6, la resta de dades s'envien al nucli del sistema operatiu mitjançant UART3 en temps real amb una freqüència de mostreig de 16 KHz.AD1 i AD5 es poden utilitzar en paral·lel, i AD3 i AD7 es poden utilitzar en paral·lel, la qual cosa equival a dos AD de mostreig de 32 KHz.AD1, AD3, AD5, AD7 es poden utilitzar en paral·lel, la qual cosa equival a un AD de mostreig de 64 KHz;les dades es sumen 1024 vegades i després es divideixen per 64 per obtenir un valor AD de 64 Hz de 16 bits mitjançant un sobremostreig. |

| 7 | AD6 | I | |

| 8 | AD5 | I | |

| 9 | AD3 | I | |

| 10 | AD2 | I | |

| 11 | 3.3 | O | Sortida de 3,3 V, càrrega màxima de 150 mA. |

| 12 | SPK | O | MOSFET extern per conduir el timbre o l'altaveu.La resistència externa de 10K s'ha de tirar cap a terra per assegurar-se que l'engegada sigui baix. |

| 13 | SD_CD | E/S | Interfície SD/SDHC, el SD_CK connecta un condensador de 22pF a GND a prop de la interfície de la targeta SD. |

| 14 | SD_CK | O | |

| 15 | SD_D3 | E/S | |

| 16 | SD_D2 | E/S | |

| 17 | SD_D1 | E/S | |

| 18 | SD_D0 | E/S | |

| 19 | PWM0 | O | 2 Sortides PWM de 16 bits.La resistència externa de 10K s'ha de tirar cap a terra per assegurar-se que l'engegada sigui baix. El nucli del sistema operatiu es pot controlar en temps real mitjançant UART3 |

| 20 | PWM1 | O | |

| 21 | P3.3 | E/S | Si utilitzeu RX8130 o SD2058 I2C RTC per connectar-se a ambdues IO, SCL s'hauria de connectar a P3.2 i SDA connectat a P3.3 en paral·lel amb una resistència de 10K a 3,3V. |

| 22 | P3.2 | E/S | |

| 23 | P3.1/EX1 | E/S | Es pot utilitzar com a entrada d'interrupció externa 1 al mateix temps i admet tant els modes d'interrupció de nivell de baixa tensió com el de vora posterior. |

| 24 | P3.0/EX0 | E/S | Es pot utilitzar com a entrada d'interrupció externa 0 al mateix temps i admet tant els modes d'interrupció de nivell de baixa tensió com el de vora posterior. |

| 25 | P2.7 | E/S | Interfície IO |

| 26 | P2.6 | E/S | Interfície IO |

| 27 | P2.5 | E/S | Interfície IO |

| 28 | P2.4 | E/S | Interfície IO |

| 29 | P2.3 | E/S | Interfície IO |

| 30 | P2.2 | E/S | Interfície IO |

| 31 | P2.1 | E/S | Interfície IO |

| 32 | P2.0 | E/S | Interfície IO |

| 33 | P1.7 | E/S | Interfície IO |

| 34 | P1.6 | E/S | Interfície IO |

| 35 | P1.5 | E/S | Interfície IO |

| 36 | P1.4 | E/S | Interfície IO |

| 37 | P1.3 | E/S | Interfície IO |

| 38 | P1.2 | E/S | Interfície IO |

| 39 | P1.1 | E/S | Interfície IO |

| 40 | P1.0 | E/S | Interfície IO |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | I | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | I | |

| 45 | P0.0 | E/S | Interfície IO |

| 46 | P0.1 | E/S | Interfície IO |

| 47 | CAN_TX | O | Interfície CAN |

| 48 | CAN_RX | I | |

| 49 | UART2_TXD | O | UART2 (port sèrie UART0 del nucli del sistema operatiu) |

| 50 | UART2_RXD | I |